## IA-32 Intel<sup>®</sup> Architecture Software Developer's Manual

### Volume 2B: Instruction Set Reference, N-Z

**NOTE**: The *IA-32 Intel Architecture Software Developer's Manual* consists of four volumes: *Basic Architecture*, Order Number 253665; *Instruction Set Reference A-M*, Order Number 253666; *Instruction Set Reference N-Z*, Order Number 253667; and the *System Programming Guide*, Order Number 253668. Refer to all four volumes when evaluating your design needs.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice.

Developers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Improper use of reserved or undefined features or instructions may cause unpredictable behavior or failure in developer's software code when running on an Intel processor. Intel reserves these features or instructions for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from their unauthorized use.

The Intel<sup>®</sup> IA-32 architecture processors (e.g., Pentium<sup>®</sup> 4 and Pentium III processors) may contain design defects or errors known as errata. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting Hyper-Threading Technology and an HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/info/hyperthreading/ for more information including details on which processors support HT Technology.

Intel, Intel386, Intel486, Pentium, Intel Xeon, Intel NetBurst, Intel SpeedStep, OverDrive, MMX, Celeron, and Itanium are trademarks or registered trademarks of Intel Corporation and its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call 1-800-548-4725 or visit Intel's website at http://www.intel.com

Copyright © 1997 - 2004 Intel Corporation

4

# **Instruction Set Reference, N-Z**

### CHAPTER 4 INSTRUCTION SET REFERENCE, N-Z

Chapter 4 continues the alphabetical discussion of IA-32 instructions (N-Z) started in Chapter 3. To access information on the remainder of the IA-32 instructions (A-M), see *IA-32 Intel Architecture Software Developer's Manual, Volume 2A.*

### **NEG—Two's Complement Negation**

| Opcode | Instruction     | Description                    |  |

|--------|-----------------|--------------------------------|--|

| F6 /3  | NEG <i>r/m8</i> | Two's complement negate r/m8.  |  |

| F7 /3  | NEG r/m16       | Two's complement negate r/m16. |  |

| F7 /3  | NEG r/m32       | Two's complement negate r/m32. |  |

#### Description

Replaces the value of operand (the destination operand) with its two's complement. (This operation is equivalent to subtracting the operand from 0.) The destination operand is located in a general-purpose register or a memory location.

This instruction can be used with a LOCK prefix to allow the instruction to be executed atomically.

#### Operation

```

IF DEST = 0

THEN CF \leftarrow 0

ELSE CF \leftarrow 1;

FI;

DEST \leftarrow - (DEST)

```

#### **Flags Affected**

The CF flag set to 0 if the source operand is 0; otherwise it is set to 1. The OF, SF, ZF, AF, and PF flags are set according to the result.

#### **Protected Mode Exceptions**

#GP(0) If the destination is located in a non-writable segment.

If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.

If the DS, ES, FS, or GS register contains a null segment selector.

#### **INSTRUCTION SET REFERENCE, N-Z**

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                             |

|-----------------|--------------------------------------------------------------------------------------------------------------------|

| #PF(fault-code) | If a page fault occurs.                                                                                            |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3. |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit. |

|-----|-------------------------------------------------------------------------------------------|

| #SS | If a memory operand effective address is outside the SS segment limit.                    |

#### Virtual-8086 Mode Exceptions

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit. |

|-----------------|-------------------------------------------------------------------------------------------|

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                    |

| #PF(fault-code) | If a page fault occurs.                                                                   |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is made.               |

### **NOP—No Operation**

| Opcode | Instruction | Description   |

|--------|-------------|---------------|

| 90     | NOP         | No operation. |

#### Description

Performs no operation. This instruction is a one-byte instruction that takes up space in the instruction stream but does not affect the machine context, except the EIP register.

The NOP instruction is an alias mnemonic for the XCHG (E)AX, (E)AX instruction.

#### **Flags Affected**

None.

#### **Exceptions (All Operating Modes)**

None.

### **NOT—One's Complement Negation**

| Opcode | Instruction      | Description                |  |

|--------|------------------|----------------------------|--|

| F6 /2  | NOT <i>r/m8</i>  | Reverse each bit of r/m8.  |  |

| F7 /2  | NOT <i>r/m16</i> | Reverse each bit of r/m16. |  |

| F7 /2  | NOT <i>r/m32</i> | Reverse each bit of r/m32. |  |

#### Description

Performs a bitwise NOT operation (each 1 is set to 0, and each 0 is set to 1) on the destination operand and stores the result in the destination operand location. The destination operand can be a register or a memory location.

This instruction can be used with a LOCK prefix to allow the instruction to be executed atomically.

#### Operation

$\mathsf{DEST} \gets \mathsf{NOT} \ \mathsf{DEST};$

#### **Flags Affected**

None.

#### **Protected Mode Exceptions**

| #GP(0)          | If the destination operand points to a non-writable segment.                                                          |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|--|

|                 | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.                             |  |

|                 | If the DS, ES, FS, or GS register contains a null segment selector.                                                   |  |

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                                |  |

| #PF(fault-code) | If a page fault occurs.                                                                                               |  |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is<br>made while the current privilege level is 3. |  |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit. |

|-----|-------------------------------------------------------------------------------------------|

| #SS | If a memory operand effective address is outside the SS segment limit.                    |

### Virtual-8086 Mode Exceptions

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit. |

|-----------------|-------------------------------------------------------------------------------------------|

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                    |

| #PF(fault-code) | If a page fault occurs.                                                                   |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is made.               |

| <b>OR</b> —Logical | <b>Inclusive OR</b> |

|--------------------|---------------------|

|--------------------|---------------------|

| Opcode          | Instruction         | Description                    |

|-----------------|---------------------|--------------------------------|

| 0C ib           | OR AL, <i>imm8</i>  | AL OR imm8.                    |

| 0D <i>iw</i>    | OR AX,imm16         | AX OR imm16.                   |

| 0D <i>id</i>    | OR EAX,imm32        | EAX OR imm32.                  |

| 80 /1 <i>ib</i> | OR r/m8,imm8        | r/m8 OR imm8.                  |

| 81 /1 <i>iw</i> | OR r/m16,imm16      | r/m16 OR imm16.                |

| 81 /1 <i>id</i> | OR r/m32,imm32      | r/m32 OR imm32                 |

| 83 /1 <i>ib</i> | OR                  | r/m16 OR imm8 (sign-extended). |

| 83 /1 <i>ib</i> | OR r/m32,imm8       | r/m32 OR imm8 (sign-extended). |

| 08 /r           | OR <i>r/m8,r8</i>   | r/m8 OR r8.                    |

| 09 /r           | OR <i>r/m16,r16</i> | r/m16 OR r16.                  |

| 09 /r           | OR r/m32,r32        | r/m32 OR r32.                  |

| 0A / <i>r</i>   | OR <i>r8,r/m8</i>   | r8 OR r/m8.                    |

| 0B / <i>r</i>   | OR r16,r/m16        | r16 OR r/m16.                  |

| 0B / <i>r</i>   | OR r32,r/m32        | r32 OR r/m32.                  |

#### Description

Performs a bitwise inclusive OR operation between the destination (first) and source (second) operands and stores the result in the destination operand location. The source operand can be an immediate, a register, or a memory location; the destination operand can be a register or a memory location. (However, two memory operands cannot be used in one instruction.) Each bit of the result of the OR instruction is set to 0 if both corresponding bits of the first and second operands are 0; otherwise, each bit is set to 1.

This instruction can be used with a LOCK prefix to allow the instruction to be executed atomically.

#### Operation

DEST ← DEST OR SRC;

#### **Flags Affected**

The OF and CF flags are cleared; the SF, ZF, and PF flags are set according to the result. The state of the AF flag is undefined.

#### **Protected Mode Exceptions**

#GP(0) If the destination operand points to a non-writable segment.

If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.

If the DS, ES, FS, or GS register contains a null segment selector.

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                             |

|-----------------|--------------------------------------------------------------------------------------------------------------------|

| #PF(fault-code) | If a page fault occurs.                                                                                            |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3. |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand effective address is outside the CS, DS, ES, FS, c |  |

|-----|------------------------------------------------------------------------|--|

|     | GS segment limit.                                                      |  |

#SS If a memory operand effective address is outside the SS segment limit.

#### Virtual-8086 Mode Exceptions

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit. |  |

|-----------------|-------------------------------------------------------------------------------------------|--|

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                    |  |

| #PF(fault-code) | If a page fault occurs.                                                                   |  |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is made.               |  |

# ORPD—Bitwise Logical OR of Double-Precision Floating-Point Values

Opcode

Instruction

Description

66 0F 56 /r

ORPD xmm1, xmm2/m128

Bitwise OR of xmm2/m128 and xmm1.

#### Description

Performs a bitwise logical OR of the two packed double-precision floating-point values from the source operand (second operand) and the destination operand (first operand), and stores the result in the destination operand. The source operand can be an XMM register or a 128-bit memory location. The destination operand is an XMM register.

#### Operation

$DEST[127-0] \leftarrow DEST[127-0]$  BitwiseOR SRC[127-0];

#### Intel C/C++ Compiler Intrinsic Equivalent

ORPD \_\_m128d \_mm\_or\_pd(\_\_m128d a, \_\_m128d b)

#### **SIMD Floating-Point Exceptions**

None.

#### **Protected Mode Exceptions**

| #GP(0)          | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |

|-----------------|---------------------------------------------------------------------------------------|

|                 | If a memory operand is not aligned on a 16-byte boundary, regardless of segment.      |

| #SS(0)          | For an illegal address in the SS segment.                                             |

| #PF(fault-code) | For a page fault.                                                                     |

| #NM             | If TS in CR0 is set.                                                                  |

| #UD             | If EM in CR0 is set.                                                                  |

|                 | If OSFXSR in CR4 is 0.                                                                |

|                 | If CPUID feature flag SSE2 is 0.                                                      |

|                 |                                                                                       |

#### **Real-Address Mode Exceptions**

| #GP(0) | If a memory operand is not aligned on a 16-byte boundary, regardless of segment.     |  |

|--------|--------------------------------------------------------------------------------------|--|

|        | If any part of the operand lies outside the effective address space from 0 to FFFFH. |  |

| #NM    | If TS in CR0 is set.                                                                 |  |

| #UD    | If EM in CR0 is set.                                                                 |  |

|        | If OSFXSR in CR4 is 0.                                                               |  |

|        | If CPUID feature flag SSE2 is 0.                                                     |  |

|        |                                                                                      |  |

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

#PF(fault-code) For a page fault.

# ORPS—Bitwise Logical OR of Single-Precision Floating-Point Values

| Opcode   | Instruction          | Description                       |

|----------|----------------------|-----------------------------------|

| 0F 56 /r | ORPS xmm1, xmm2/m128 | Bitwise OR of xmm2/m128 and xmm1. |

#### Description

Performs a bitwise logical OR of the four packed single-precision floating-point values from the source operand (second operand) and the destination operand (first operand), and stores the result in the destination operand. The source operand can be an XMM register or a 128-bit memory location. The destination operand is an XMM register.

#### Operation

$DEST[127-0] \leftarrow DEST[127-0]$  BitwiseOR SRC[127-0];

#### Intel C/C++ Compiler Intrinsic Equivalent

ORPS \_\_m128 \_mm\_or\_ps(\_\_m128 a, \_\_m128 b)

#### SIMD Floating-Point Exceptions

None.

#### **Protected Mode Exceptions**

| #GP(0)          | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |  |

|-----------------|---------------------------------------------------------------------------------------|--|

|                 | If a memory operand is not aligned on a 16-byte boundary, regardless of segment.      |  |

| #SS(0)          | For an illegal address in the SS segment.                                             |  |

| #PF(fault-code) | For a page fault.                                                                     |  |

| #NM             | If TS in CR0 is set.                                                                  |  |

| #UD             | If EM in CR0 is set.                                                                  |  |

|                 | If OSFXSR in CR4 is 0.                                                                |  |

|                 | If CPUID feature flag SSE is 0.                                                       |  |

|                 |                                                                                       |  |

#### **Real-Address Mode Exceptions**

#GP(0) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.

#UD

If any part of the operand lies outside the effective address space from 0 to FFFFH.

#NM If TS in CR0 is set.

If EM in CR0 is set.

If OSFXSR in CR4 is 0.

If CPUID feature flag SSE is 0.

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

#PF(fault-code) For a page fault.

| Opcode | Instruction   | Description                                         |

|--------|---------------|-----------------------------------------------------|

| E6 ib  | OUT imm8, AL  | Output byte in AL to I/O port address imm8.         |

| E7 ib  | OUT imm8, AX  | Output word in AX to I/O port address imm8.         |

| E7 ib  | OUT imm8, EAX | Output doubleword in EAX to I/O port address imm8.  |

| EE     | OUT DX, AL    | Output byte in AL to I/O port address in DX.        |

| EF     | OUT DX, AX    | Output word in AX to I/O port address in DX.        |

| EF     | OUT DX, EAX   | Output doubleword in EAX to I/O port address in DX. |

### **OUT—Output to Port**

#### Description

Copies the value from the second operand (source operand) to the I/O port specified with the destination operand (first operand). The source operand can be register AL, AX, or EAX, depending on the size of the port being accessed (8, 16, or 32 bits, respectively); the destination operand can be a byte-immediate or the DX register. Using a byte immediate allows I/O port addresses 0 to 255 to be accessed; using the DX register as a source operand allows I/O ports from 0 to 65,535 to be accessed.

The size of the I/O port being accessed is determined by the opcode for an 8-bit I/O port or by the operand-size attribute of the instruction for a 16- or 32-bit I/O port.

At the machine code level, I/O instructions are shorter when accessing 8-bit I/O ports. Here, the upper eight bits of the port address will be 0.

This instruction is only useful for accessing I/O ports located in the processor's I/O address space. See Chapter 13, *Input/Output*, in the *IA-32 Intel Architecture Software Developer's Manual, Volume 1*, for more information on accessing I/O ports in the I/O address space.

#### IA-32 Architecture Compatibility

After executing an OUT instruction, the Pentium processor insures that the EWBE# pin has been sampled active before it begins to execute the next instruction. (Note that the instruction can be prefetched if EWBE# is not active, but it will not be executed until the EWBE# pin is sampled active.) Only the Pentium processor family has the EWBE# pin; the other IA-32 processors do not.

#### Operation

```

\begin{array}{l} \mathsf{IF} \; ((\mathsf{PE}=1) \; \mathsf{AND} \; ((\mathsf{CPL} > \mathsf{IOPL}) \; \mathsf{OR} \; (\mathsf{VM}=1))) \\ \mathsf{THEN} \; (* \; \mathsf{Protected} \; \mathsf{mode} \; \mathsf{with} \; \mathsf{CPL} > \mathsf{IOPL} \; \mathsf{or} \; \mathsf{virtual}{=}8086 \; \mathsf{mode} \; *) \\ \mathsf{IF} \; (\mathsf{Any} \; \mathsf{I/O} \; \mathsf{Permission} \; \mathsf{Bit} \; \mathsf{for} \; \mathsf{I/O} \; \mathsf{port} \; \mathsf{being} \; \mathsf{accessed} = 1) \\ \mathsf{THEN} \; (* \; \mathsf{I/O} \; \mathsf{operation} \; \mathsf{is} \; \mathsf{not} \; \mathsf{allowed} \; *) \\ \; \#\mathsf{GP}(0); \\ \mathsf{ELSE} \; ( \; * \; \mathsf{I/O} \; \mathsf{operation} \; \mathsf{is} \; \mathsf{allowed} \; *) \\ \; \mathsf{DEST} \leftarrow \; \mathsf{SRC}; \; (* \; \mathsf{Writes} \; \mathsf{to} \; \mathsf{selected} \; \mathsf{I/O} \; \mathsf{port} \; *) \\ \mathsf{FI}; \end{array}

```

```

ELSE (Real Mode or Protected Mode with CPL \leq IOPL *)

DEST \leftarrow SRC; (* Writes to selected I/O port *)

FI;

```

#### **Flags Affected**

None.

#### **Protected Mode Exceptions**

#GP(0) If the CPL is greater than (has less privilege) the I/O privilege level (IOPL) and any of the corresponding I/O permission bits in TSS for the I/O port being accessed is 1.

#### **Real-Address Mode Exceptions**

None.

#### Virtual-8086 Mode Exceptions

#GP(0) If any of the I/O permission bits in the TSS for the I/O port being accessed is 1.

### OUTS/OUTSB/OUTSW/OUTSD—Output String to Port

| Opcode | Instruction  | Description                                                                                  |

|--------|--------------|----------------------------------------------------------------------------------------------|

| 6E     | OUTS DX, m8  | Output byte from memory location specified in DS:(E)SI to I/O port specified in DX.          |

| 6F     | OUTS DX, m16 | Output word from memory location specified in DS:(E)SI to I/O port specified in DX.          |

| 6F     | OUTS DX, m32 | Output doubleword from memory location specified in<br>DS:(E)SI to I/O port specified in DX. |

| 6E     | OUTSB        | Output byte from memory location specified in DS:(E)SI to<br>I/O port specified in DX.       |

| 6F     | OUTSW        | Output word from memory location specified in DS:(E)SI to I/O port specified in DX.          |

| 6F     | OUTSD        | Output doubleword from memory location specified in<br>DS:(E)SI to I/O port specified in DX. |

#### Description

Copies data from the source operand (second operand) to the I/O port specified with the destination operand (first operand). The source operand is a memory location, the address of which is read from either the DS:ESI or the DS:SI registers (depending on the address-size attribute of the instruction, 32 or 16, respectively). (The DS segment may be overridden with a segment override prefix.) The destination operand is an I/O port address (from 0 to 65,535) that is read from the DX register. The size of the I/O port being accessed (that is, the size of the source and destination operands) is determined by the opcode for an 8-bit I/O port or by the operand-size attribute of the instruction for a 16- or 32-bit I/O port.

At the assembly-code level, two forms of this instruction are allowed: the "explicit-operands" form and the "no-operands" form. The explicit-operands form (specified with the OUTS mnemonic) allows the source and destination operands to be specified explicitly. Here, the source operand should be a symbol that indicates the size of the I/O port and the source address, and the destination operand must be DX. This explicit-operands form is provided to allow documentation; however, note that the documentation provided by this form can be misleading. That is, the source operand symbol must specify the correct **type** (size) of the operand (byte, word, or doubleword), but it does not have to specify the correct **location**. The location is always specified by the DS:(E)SI registers, which must be loaded correctly before the OUTS instruction is executed.

The no-operands form provides "short forms" of the byte, word, and doubleword versions of the OUTS instructions. Here also DS:(E)SI is assumed to be the source operand and DX is assumed to be the destination operand. The size of the I/O port is specified with the choice of mnemonic: OUTSB (byte), OUTSW (word), or OUTSD (doubleword).

After the byte, word, or doubleword is transferred from the memory location to the I/O port, the (E)SI register is incremented or decremented automatically according to the setting of the DF flag in the EFLAGS register. (If the DF flag is 0, the (E)SI register is incremented; if the DF flag is 1, the (E)SI register is decremented.) The (E)SI register is incremented or decremented by 1 for byte operations, by 2 for word operations, or by 4 for doubleword operations.

The OUTS, OUTSB, OUTSW, and OUTSD instructions can be preceded by the REP prefix for block input of ECX bytes, words, or doublewords. See "REP/REPE/REPZ/REPNE /REPNZ—Repeat String Operation Prefix" in this chapter for a description of the REP prefix. This instruction is only useful for accessing I/O ports located in the processor's I/O address space. See Chapter 13, *Input/Output*, in the *IA-32 Intel Architecture Software Developer's Manual, Volume 1*, for more information on accessing I/O ports in the I/O address space.

#### IA-32 Architecture Compatibility

After executing an OUTS, OUTSB, OUTSW, or OUTSD instruction, the Pentium processor insures that the EWBE# pin has been sampled active before it begins to execute the next instruction. (Note that the instruction can be prefetched if EWBE# is not active, but it will not be executed until the EWBE# pin is sampled active.) Only the Pentium processor family has the EWBE# pin; the other IA-32 processors do not. For the Pentium 4, Intel Xeon, and P6 family processors, upon execution of an OUTS, OUTSB, OUTSB, OUTSW, or OUTSD instruction, the processor will not execute the next instruction until the data phase of the transaction is complete.

#### Operation

```

IF ((PE = 1) AND ((CPL > IOPL) OR (VM = 1)))

THEN (* Protected mode with CPL > IOPL or virtual-8086 mode *)

IF (Any I/O Permission Bit for I/O port being accessed = 1)

THEN (* I/O operation is not allowed *)

#GP(0);

ELSE (* I/O operation is allowed *)

DEST ← SRC; (* Writes to I/O port *)

FI:

ELSE (Real Mode or Protected Mode with CPL \leq IOPL *)

DEST \leftarrow SRC; (* Writes to I/O port *)

FI:

IF (byte transfer)

THEN IF DF = 0

THEN (E)SI \leftarrow (E)SI + 1;

ELSE (E)SI \leftarrow (E)SI – 1;

FI;

ELSE IF (word transfer)

THEN IF DF = 0

THEN (E)SI \leftarrow (E)SI + 2;

ELSE (E)SI \leftarrow (E)SI – 2;

FI;

ELSE (* doubleword transfer *)

THEN IF DF = 0

THEN (E)SI \leftarrow (E)SI + 4;

ELSE (E)SI \leftarrow (E)SI – 4;

FI; FI; FI;

```

#### **Flags Affected**

None.

#### **Protected Mode Exceptions**

| #GP(0)          | If the CPL is greater than (has less privilege) the I/O privilege level (IOPL) and any of the corresponding I/O permission bits in TSS for the I/O port being accessed is 1. |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | If a memory operand effective address is outside the limit of the CS, DS, ES, FS, or GS segment.                                                                             |  |

|                 | If the segment register contains a null segment selector.                                                                                                                    |  |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                                      |  |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3.                                                           |  |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit. |

|-----|-------------------------------------------------------------------------------------------|

| #SS | If a memory operand effective address is outside the SS segment limit.                    |

### Virtual-8086 Mode Exceptions

| #GP(0)          | If any of the I/O permission bits in the TSS for the I/O port being accessed is 1. |

|-----------------|------------------------------------------------------------------------------------|

| #PF(fault-code) | If a page fault occurs.                                                            |

| #AC(0)          | If alignment checking is enabled and an unaligned memory reference is made.        |

### PACKSSWB/PACKSSDW—Pack with Signed Saturation

| Opcode      | Instruction              | Description                                                                                                                                                        |

|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0F 63 /r    | PACKSSWB mm1, mm2/m64    | Converts 4 packed signed word integers from <i>mm1</i> and from <i>mm2/m64</i> into 8 packed signed byte integers in <i>mm1</i> using signed saturation.           |

| 66 0F 63 /r | PACKSSWB xmm1, xmm2/m128 | Converts 8 packed signed word integers from <i>xmm1</i> and from <i>xmm2/m128</i> into 16 packed signed byte integers in <i>xmm1</i> using signed saturation.      |

| 0F 6B /r    | PACKSSDW mm1, mm2/m64    | Converts 2 packed signed doubleword integers from <i>mm1</i> and from <i>mm2/m64</i> into 4 packed signed word integers in <i>mm1</i> using signed saturation.     |

| 66 0F 6B /r | PACKSSDW xmm1, xmm2/m128 | Converts 4 packed signed doubleword integers from <i>xmm1</i> and from <i>xmm2/m128</i> into 8 packed signed word integers in <i>xmm1</i> using signed saturation. |

#### Description

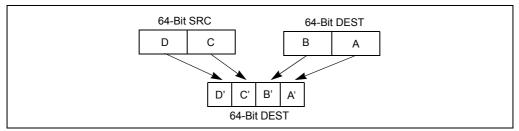

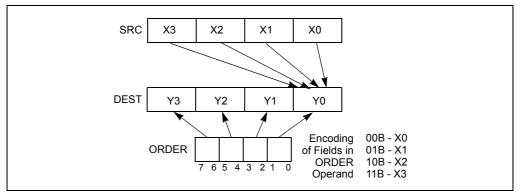

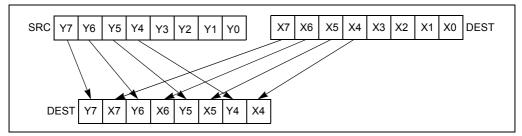

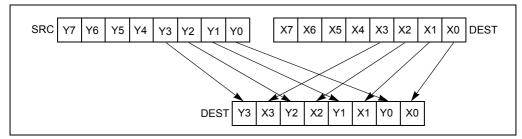

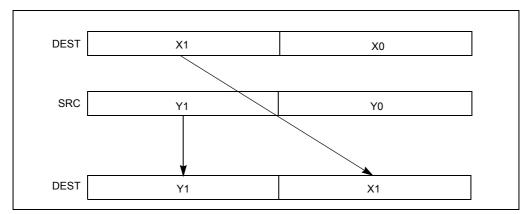

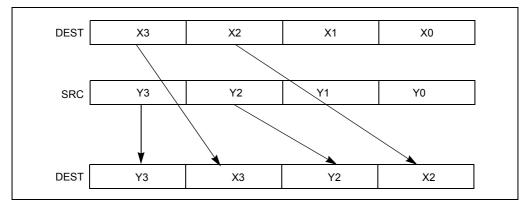

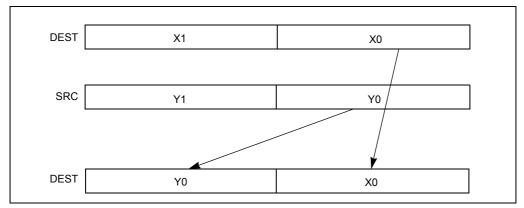

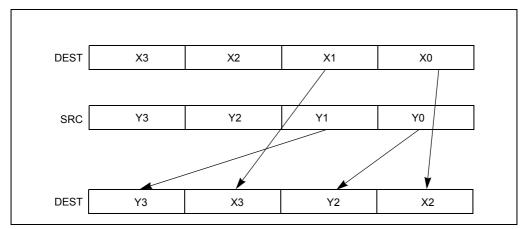

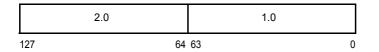

Converts packed signed word integers into packed signed byte integers (PACKSSWB) or converts packed signed doubleword integers into packed signed word integers (PACKSSDW), using saturation to handle overflow conditions. See Figure 4-1 for an example of the packing operation.

Figure 4-1. Operation of the PACKSSDW Instruction Using 64-bit Operands.

The PACKSSWB instruction converts 4 or 8 signed word integers from the destination operand (first operand) and 4 or 8 signed word integers from the source operand (second operand) into 8 or 16 signed byte integers and stores the result in the destination operand. If a signed word integer value is beyond the range of a signed byte integer (that is, greater than 7FH for a positive integer or greater than 80H for a negative integer), the saturated signed byte integer value of 7FH or 80H, respectively, is stored in the destination.

The PACKSSDW instruction packs 2 or 4 signed doublewords from the destination operand (first operand) and 2 or 4 signed doublewords from the source operand (second operand) into 4 or 8 signed words in the destination operand (see Figure 4-1). If a signed doubleword integer

value is beyond the range of a signed word (that is, greater than 7FFFH for a positive integer or greater than 8000H for a negative integer), the saturated signed word integer value of 7FFFH or 8000H, respectively, is stored into the destination.

The PACKSSWB and PACKSSDW instructions operate on either 64-bit or 128-bit operands. When operating on 64-bit operands, the destination operand must be an MMX technology register and the source operand can be either an MMX technology register or a 64-bit memory location. When operating on 128-bit operands, the destination operand must be an XMM register and the source operand can be either an XMM register or a 128-bit memory location.

#### Operation

PACKSSWB instruction with 64-bit operands

DEST[7..0]  $\leftarrow$  SaturateSignedWordToSignedByte DEST[15..0]; DEST[15..8]  $\leftarrow$  SaturateSignedWordToSignedByte DEST[31..16]; DEST[23..16]  $\leftarrow$  SaturateSignedWordToSignedByte DEST[47..32]; DEST[31..24] ← SaturateSignedWordToSignedByte DEST[63..48]; DEST[39..32] ← SaturateSignedWordToSignedByte SRC[15..0]; DEST[47..40]  $\leftarrow$  SaturateSignedWordToSignedByte SRC[31..16]; DEST[55..48]  $\leftarrow$  SaturateSignedWordToSignedByte SRC[47..32]; DEST[63..56]  $\leftarrow$  SaturateSignedWordToSignedByte SRC[63..48]; PACKSSDW instruction with 64-bit operands DEST[15..0]  $\leftarrow$  SaturateSignedDoublewordToSignedWord DEST[31..0]; DEST[31..16]  $\leftarrow$  SaturateSignedDoublewordToSignedWord DEST[63..32]: DEST[47..32] ← SaturateSignedDoublewordToSignedWord SRC[31..0]; DEST[63..48] ← SaturateSignedDoublewordToSignedWord SRC[63..32]; PACKSSWB instruction with 128-bit operands DEST[7-0]  $\leftarrow$  SaturateSignedWordToSignedByte (DEST[15-0]); DEST[15-8]  $\leftarrow$  SaturateSignedWordToSignedByte (DEST[31-16]); DEST[23-16]  $\leftarrow$  SaturateSignedWordToSignedByte (DEST[47-32]); DEST[31-24]  $\leftarrow$  SaturateSignedWordToSignedByte (DEST[63-48]); DEST[39-32]  $\leftarrow$  SaturateSignedWordToSignedByte (DEST[79-64]); DEST[47-40]  $\leftarrow$  SaturateSignedWordToSignedByte (DEST[95-80]);  $DEST[55-48] \leftarrow SaturateSignedWordToSignedByte (DEST[111-96]);$ DEST[63-56]  $\leftarrow$  SaturateSignedWordToSignedByte (DEST[127-112]); DEST[71-64]  $\leftarrow$  SaturateSignedWordToSignedByte (SRC[15-0]); DEST[79-72]  $\leftarrow$  SaturateSignedWordToSignedByte (SRC[31-16]); DEST[87-80]  $\leftarrow$  SaturateSignedWordToSignedByte (SRC[47-32]); DEST[95-88] ← SaturateSignedWordToSignedByte (SRC[63-48]); DEST[103-96]  $\leftarrow$  SaturateSignedWordToSignedByte (SRC[79-64]); DEST[111-104]  $\leftarrow$  SaturateSignedWordToSignedByte (SRC[95-80]); DEST[119-112] ← SaturateSignedWordToSignedByte (SRC[111-96]); DEST[127-120]  $\leftarrow$  SaturateSignedWordToSignedByte (SRC[127-112]);

PACKSSDW instruction with 128-bit operands

DEST[15-0]  $\leftarrow$  SaturateSignedDwordToSignedWord (DEST[31-0]);

$\begin{array}{l} \mathsf{DEST}[31\text{-}16] \leftarrow \mathsf{SaturateSignedDwordToSignedWord} \ (\mathsf{DEST}[63\text{-}32]);\\ \mathsf{DEST}[47\text{-}32] \leftarrow \mathsf{SaturateSignedDwordToSignedWord} \ (\mathsf{DEST}[95\text{-}64]);\\ \mathsf{DEST}[63\text{-}48] \leftarrow \mathsf{SaturateSignedDwordToSignedWord} \ (\mathsf{DEST}[127\text{-}96]);\\ \mathsf{DEST}[79\text{-}64] \leftarrow \mathsf{SaturateSignedDwordToSignedWord} \ (\mathsf{SRC}[31\text{-}0]);\\ \mathsf{DEST}[95\text{-}80] \leftarrow \mathsf{SaturateSignedDwordToSignedWord} \ (\mathsf{SRC}[63\text{-}32]);\\ \mathsf{DEST}[111\text{-}96] \leftarrow \mathsf{SaturateSignedDwordToSignedWord} \ (\mathsf{SRC}[95\text{-}64]);\\ \mathsf{DEST}[127\text{-}112] \leftarrow \mathsf{SaturateSignedDwordToSignedWord} \ (\mathsf{SRC}[127\text{-}96]); \end{array}$

#### Intel C/C++ Compiler Intrinsic Equivalents

\_\_m64 \_mm\_packs\_pi16(\_\_m64 m1, \_\_m64 m2) \_\_m64 \_mm\_packs\_pi32 (\_\_m64 m1, \_\_m64 m2)

#### **Flags Affected**

None.

#### **Protected Mode Exceptions**

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.                                                   |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.                                  |  |

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                                                      |  |

| #UD             | If EM in CR0 is set.                                                                                                                        |  |

|                 | (128-bit operations only) If OSFXSR in CR4 is 0.                                                                                            |  |

| #NM             | If TS in CR0 is set.                                                                                                                        |  |

| #MF             | (64-bit operations only) If there is a pending x87 FPU exception.                                                                           |  |

| #PF(fault-code) | If a page fault occurs.                                                                                                                     |  |

| #AC(0)          | (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3. |  |

#### **Real-Address Mode Exceptions**

| #GP(0) | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment. |

|--------|------------------------------------------------------------------------------------------------------------|

|        | If any part of the operand lies outside of the effective address space from 0 to FFFFH.                    |

| #UD    | If EM in CR0 is set.                                                                                       |

|        | (128-bit operations only) If OSFXSR in CR4 is 0.                                                           |

|        |                                                                                                            |

#MF (64-bit operations only) If there is a pending x87 FPU exception.

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

- #PF(fault-code) For a page fault.

- #AC(0) (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made.

### PACKUSWB—Pack with Unsigned Saturation

| Opcode      | Instruction              | Description                                                                                                                                                                |

|-------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0F 67 /r    | PACKUSWB mm, mm/m64      | Converts 4 signed word integers from <i>mm</i> and 4 signed word integers from <i>mm/m64</i> into 8 unsigned byte integers in <i>mm</i> using unsigned saturation.         |

| 66 0F 67 /r | PACKUSWB xmm1, xmm2/m128 | Converts 8 signed word integers from <i>xmm1</i> and 8 signed word integers from <i>xmm2/m128</i> into 16 unsigned byte integers in <i>xmm1</i> using unsigned saturation. |

#### Description

Converts 4 or 8 signed word integers from the destination operand (first operand) and 4 or 8 signed word integers from the source operand (second operand) into 8 or 16 unsigned byte integers and stores the result in the destination operand. (See Figure 4-1 for an example of the packing operation.) If a signed word integer value is beyond the range of an unsigned byte integer (that is, greater than FFH or less than 00H), the saturated unsigned byte integer value of FFH or 00H, respectively, is stored in the destination.

The PACKUSWB instruction operates on either 64-bit or 128-bit operands. When operating on 64-bit operands, the destination operand must be an MMX technology register and the source operand can be either an MMX technology register or a 64-bit memory location. When operating on 128-bit operands, the destination operand must be an XMM register and the source operand can be either an XMM register or a 128-bit memory location.

#### Operation

PACKUSWB instruction with 64-bit operands:

#### PACKUSWB instruction with 128-bit operands:

#### Intel C/C++ Compiler Intrinsic Equivalent

\_\_\_m64 \_mm\_packs\_pu16(\_\_m64 m1, \_\_m64 m2)

#### **Flags Affected**

None.

#### **Protected Mode Exceptions**

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.                                                                                                                                                                 |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.                                                                                                                                                |  |

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                                                                                                                                                                    |  |

| #UD             | If EM in CR0 is set.                                                                                                                                                                                                                                      |  |

|                 | 128-bit operations will generate #UD only if OSFXSR in CR4 is 0. Execu-<br>tion of 128-bit instructions on a non-SSE2 capable processor (one that is<br>MMX technology capable) will result in the instruction operating on the<br>mm registers, not #UD. |  |

| #NM             | If TS in CR0 is set.                                                                                                                                                                                                                                      |  |

| #MF             | (64-bit operations only) If there is a pending x87 FPU exception.                                                                                                                                                                                         |  |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                                                                                                                   |  |

| #AC(0)          | (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3.                                                                                                               |  |

#### **Real-Address Mode Exceptions**

#GP(0) (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.

If any part of the operand lies outside of the effective address space from 0 to FFFFH.

| #UD | If EM in CR0 is set.                                                                                                                                                                                                                                      |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 128-bit operations will generate #UD only if OSFXSR in CR4 is 0. Execu-<br>tion of 128-bit instructions on a non-SSE2 capable processor (one that is<br>MMX technology capable) will result in the instruction operating on the<br>mm registers, not #UD. |

| #NM | If TS in CR0 is set.                                                                                                                                                                                                                                      |

| #MF | (64-bit operations only) If there is a pending x87 FPU exception.                                                                                                                                                                                         |

|     |                                                                                                                                                                                                                                                           |

### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

- #PF(fault-code) For a page fault.

- #AC(0) (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made.

### PADDB/PADDW/PADDD—Add Packed Integers

| Opcode      | Instruction           | Description                                                       |

|-------------|-----------------------|-------------------------------------------------------------------|

| 0F FC /r    | PADDB mm, mm/m64      | Add packed byte integers from mm/m64 and mm.                      |

| 66 0F FC /r | PADDB xmm1,xmm2/m128  | Add packed byte integers from xmm2/m128 and xmm1.                 |

| 0F FD /r    | PADDW mm, mm/m64      | Add packed word integers from mm/m64 and mm.                      |

| 66 0F FD /r | PADDW xmm1, xmm2/m128 | Add packed word integers from <i>xmm2/m128</i> and <i>xmm1</i> .  |

| 0F FE /r    | PADDD mm, mm/m64      | Add packed doubleword integers from <i>mm/m64</i> and <i>mm</i> . |

| 66 0F FE /r | PADDD xmm1, xmm2/m128 | Add packed doubleword integers from xmm2/m128 and xmm1.           |

#### Description

Performs an SIMD add of the packed integers from the source operand (second operand) and the destination operand (first operand), and stores the packed integer results in the destination operand. See Figure 9-4 in the *IA-32 Intel Architecture Software Developer's Manual, Volume I* for an illustration of an SIMD operation. Overflow is handled with wraparound, as described in the following paragraphs.

These instructions can operate on either 64-bit or 128-bit operands. When operating on 64-bit operands, the destination operand must be an MMX technology register and the source operand can be either an MMX technology register or a 64-bit memory location. When operating on 128-bit operands, the destination operand must be an XMM register and the source operand can be either an XMM register or a 128-bit memory location.

The PADDB instruction adds packed byte integers. When an individual result is too large to be represented in 8 bits (overflow), the result is wrapped around and the low 8 bits are written to the destination operand (that is, the carry is ignored).

The PADDW instruction adds packed word integers. When an individual result is too large to be represented in 16 bits (overflow), the result is wrapped around and the low 16 bits are written to the destination operand.

The PADDD instruction adds packed doubleword integers. When an individual result is too large to be represented in 32 bits (overflow), the result is wrapped around and the low 32 bits are written to the destination operand.

Note that the PADDB, PADDW, and PADDD instructions can operate on either unsigned or signed (two's complement notation) packed integers; however, it does not set bits in the EFLAGS register to indicate overflow and/or a carry. To prevent undetected overflow conditions, software must control the ranges of values operated on.

#### Operation

PADDB instruction with 64-bit operands: DEST[7..0] ← DEST[7..0] + SRC[7..0];

```

* repeat add operation for 2nd through 7th byte *;

DEST[63..56] ← DEST[63..56] + SRC[63..56];

```

```

PADDB instruction with 128-bit operands:

DEST[7-0] ← DEST[7-0] + SRC[7-0];

* repeat add operation for 2nd through 14th byte *;

DEST[127-120] ← DEST[111-120] + SRC[127-120];

```

```

PADDW instruction with 64-bit operands:

DEST[15..0] ← DEST[15..0] + SRC[15..0];

* repeat add operation for 2nd and 3th word *;

DEST[63..48] ← DEST[63..48] + SRC[63..48];

```

PADDW instruction with 128-bit operands: DEST[15-0] ← DEST[15-0] + SRC[15-0]; \* repeat add operation for 2nd through 7th word \*; DEST[127-112] ← DEST[127-112] + SRC[127-112];

#### PADDD instruction with 64-bit operands:

```

DEST[31..0] ← DEST[31..0] + SRC[31..0];

DEST[63..32] ← DEST[63..32] + SRC[63..32];

```

PADDD instruction with 128-bit operands: DEST[31-0] ← DEST[31-0] + SRC[31-0]; \* repeat add operation for 2nd and 3th doubleword \*; DEST[127-96] ← DEST[127-96] + SRC[127-96];

#### Intel C/C++ Compiler Intrinsic Equivalents

| PADDB | m64 _mm_add_pi8(m64 m1,m64 m2)        |

|-------|---------------------------------------|

| PADDB | m128i_mm_add_epi8 (m128ia,m128ib )    |

| PADDW | m64 _mm_addw_pi16(m64 m1,m64 m2)      |

| PADDW | m128i _mm_add_epi16 (m128i a,m128i b) |

| PADDD | m64 _mm_add_pi32(m64 m1,m64 m2)       |

| PADDD | m128i _mm_add_epi32 (m128i a,m128i b) |

#### Flags Affected

None.

#### Protected Mode Exceptions

#GP(0)

If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.

(128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.

#### **INSTRUCTION SET REFERENCE, N-Z**

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                                                                                                                                                                    |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| #UD             | If EM in CR0 is set.                                                                                                                                                                                                                                      |  |

|                 | 128-bit operations will generate #UD only if OSFXSR in CR4 is 0. Execu-<br>tion of 128-bit instructions on a non-SSE2 capable processor (one that is<br>MMX technology capable) will result in the instruction operating on the<br>mm registers, not #UD. |  |

| #NM             | If TS in CR0 is set.                                                                                                                                                                                                                                      |  |

| #MF             | (64-bit operations only) If there is a pending x87 FPU exception.                                                                                                                                                                                         |  |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                                                                                                                   |  |

| #AC(0)          | (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3.                                                                                                               |  |

#### **Real-Address Mode Exceptions**

| #GP(0) | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.                                                                                                                                                |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | If any part of the operand lies outside of the effective address space from 0 to FFFFH.                                                                                                                                                                   |  |

| #UD    | If EM in CR0 is set.                                                                                                                                                                                                                                      |  |

|        | 128-bit operations will generate #UD only if OSFXSR in CR4 is 0. Execu-<br>tion of 128-bit instructions on a non-SSE2 capable processor (one that is<br>MMX technology capable) will result in the instruction operating on the<br>mm registers, not #UD. |  |

| #NM    | If TS in CR0 is set.                                                                                                                                                                                                                                      |  |

| #MF    | (64-bit operations only) If there is a pending x87 FPU exception.                                                                                                                                                                                         |  |

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

#PF(fault-code) For a page fault.

#AC(0) (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made.

### PADDQ—Add Packed Quadword Integers

| Opcode      | Instruction          | Description                                     |

|-------------|----------------------|-------------------------------------------------|

| 0F D4 /r    | PADDQ mm1,mm2/m64    | Add quadword integer mm2/m64 to mm1.            |

| 66 0F D4 /r | PADDQ xmm1,xmm2/m128 | Add packed quadword integers xmm2/m128 to xmm1. |

#### Description

Adds the first operand (destination operand) to the second operand (source operand) and stores the result in the destination operand. The source operand can be a quadword integer stored in an MMX technology register or a 64-bit memory location, or it can be two packed quadword integers stored in an XMM register or an 128-bit memory location. The destination operand can be a quadword integer stored in an MMX technology register or two packed quadword integers stored in an XMM register. When packed quadword operands are used, an SIMD add is performed. When a quadword result is too large to be represented in 64 bits (overflow), the result is wrapped around and the low 64 bits are written to the destination element (that is, the carry is ignored).

Note that the PADDQ instruction can operate on either unsigned or signed (two's complement notation) integers; however, it does not set bits in the EFLAGS register to indicate overflow and/or a carry. To prevent undetected overflow conditions, software must control the ranges of the values operated on.

#### Operation

PADDQ instruction with 64-Bit operands: DEST[63-0] " DEST[63-0] + SRC[63-0];

PADDQ instruction with 128-Bit operands: DEST[63-0] <sup>--</sup> DEST[63-0] + SRC[63-0]; DEST[127-64] <sup>--</sup> DEST[127-64] + SRC[127-64];

#### Intel C/C++ Compiler Intrinsic Equivalents

PADDQ \_\_\_\_m64 \_mm\_add\_si64 (\_\_\_m64 a, \_\_\_m64 b) PADDQ \_\_\_\_m128i \_mm\_add\_epi64 ( \_\_\_m128i a, \_\_\_m128i b)

#### Flags Affected

None.

#### **Protected Mode Exceptions**

#GP(0)

If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.

(128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.

#### **INSTRUCTION SET REFERENCE, N-Z**

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                                                      |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| #UD             | If EM in CR0 is set.                                                                                                                        |  |

|                 | (128-bit operations only) If OSFXSR in CR4 is 0.                                                                                            |  |

|                 | (128-bit operations only) If CPUID feature flag SSE2 is 0.                                                                                  |  |

| #NM             | If TS in CR0 is set.                                                                                                                        |  |

| #MF             | (64-bit operations only) If there is a pending x87 FPU exception.                                                                           |  |

| #PF(fault-code) | If a page fault occurs.                                                                                                                     |  |

| #AC(0)          | (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3. |  |

intal

#### **Real-Address Mode Exceptions**

| #GP(0) | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment. |

|--------|------------------------------------------------------------------------------------------------------------|

|        | If any part of the operand lies outside of the effective address space from 0 to FFFFH.                    |

| #UD    | If EM in CR0 is set.                                                                                       |

|        | (128-bit operations only) If OSFXSR in CR4 is 0.                                                           |

|        | (128-bit operations only) If CPUID feature flag SSE2 is 0.                                                 |

| #NM    | If TS in CR0 is set.                                                                                       |

| #MF    | (64-bit operations only) If there is a pending x87 FPU exception.                                          |

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

| #PF(fault-code) | For a page fault. |

|-----------------|-------------------|

|-----------------|-------------------|

#AC(0) (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made.

#### **Numeric Exceptions**

None.

# PADDSB/PADDSW—Add Packed Signed Integers with Signed Saturation

| Opcode      | Instruction            | Description                                                                                     |

|-------------|------------------------|-------------------------------------------------------------------------------------------------|

| 0F EC /r    | PADDSB mm, mm/m64      | Add packed signed byte integers from <i>mm/m64 and mm</i> and saturate the results.             |

| 66 0F EC /r | PADDSB xmm1,           | Add packed signed byte integers from <i>xmm2/m128</i> and <i>xmm1</i> saturate the results.     |

| 0F ED /r    | PADDSW mm, mm/m64      | Add packed signed word integers from <i>mm/m64 and mm</i> and saturate the results.             |

| 66 0F ED /r | PADDSW xmm1, xmm2/m128 | Add packed signed word integers from <i>xmm2/m128</i> and <i>xmm1</i> and saturate the results. |

#### Description

Performs an SIMD add of the packed signed integers from the source operand (second operand) and the destination operand (first operand), and stores the packed integer results in the destination operand. See Figure 9-4 in the *IA-32 Intel Architecture Software Developer's Manual, Volume 1* for an illustration of an SIMD operation. Overflow is handled with signed saturation, as described in the following paragraphs.

These instructions can operate on either 64-bit or 128-bit operands. When operating on 64-bit operands, the destination operand must be an MMX technology register and the source operand can be either an MMX technology register or a 64-bit memory location. When operating on 128-bit operands, the destination operand must be an XMM register and the source operand can be either an XMM register or a 128-bit memory location.

The PADDSB instruction adds packed signed byte integers. When an individual byte result is beyond the range of a signed byte integer (that is, greater than 7FH or less than 80H), the saturated value of 7FH or 80H, respectively, is written to the destination operand.

The PADDSW instruction adds packed signed word integers. When an individual word result is beyond the range of a signed word integer (that is, greater than 7FFFH or less than 8000H), the saturated value of 7FFFH or 8000H, respectively, is written to the destination operand.

#### Operation

PADDSB instruction with 64-bit operands:

DEST[7..0]  $\leftarrow$  SaturateToSignedByte(DEST[7..0] + SRC (7..0]); \* repeat add operation for 2nd through 7th bytes \*; DEST[63..56]  $\leftarrow$  SaturateToSignedByte(DEST[63..56] + SRC[63..56]);

PADDSB instruction with 128-bit operands:

DEST[7-0]  $\leftarrow$  SaturateToSignedByte (DEST[7-0] + SRC[7-0]);

\* repeat add operation for 2nd through 14th bytes \*;

$DEST[127-120] \leftarrow SaturateToSignedByte (DEST[111-120] + SRC[127-120]);$

PADDSW instruction with 64-bit operands

DEST[15..0] "SaturateToSignedWord(DEST[15..0] + SRC[15..0] );

\* repeat add operation for 2nd and 7th words \*; DEST[63..48] " SaturateToSignedWord(DEST[63..48] + SRC[63..48] );

PADDSW instruction with 128-bit operands

DEST[15-0] ← SaturateToSignedWord (DEST[15-0] + SRC[15-0]); \* repeat add operation for 2nd through 7th words \*; DEST[127-112] ← SaturateToSignedWord (DEST[127-112] + SRC[127-112]);

#### Intel C/C++ Compiler Intrinsic Equivalents

| PADDSB | m64 _mm_adds_pi8(m64 m1,m64 m2)        |

|--------|----------------------------------------|

| PADDSB | m128i _mm_adds_epi8 (m128i a,m128i b)  |

| PADDSW | m64 _mm_adds_pi16(m64 m1,m64 m2)       |

| PADDSW | m128i _mm_adds_epi16 (m128i a,m128i b) |

#### **Flags Affected**

None.

#### **Protected Mode Exceptions**

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.                                                                                                                                                                 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.                                                                                                                                                |

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                                                                                                                                                                    |

| #UD             | If EM in CR0 is set.                                                                                                                                                                                                                                      |

|                 | 128-bit operations will generate #UD only if OSFXSR in CR4 is 0. Execu-<br>tion of 128-bit instructions on a non-SSE2 capable processor (one that is<br>MMX technology capable) will result in the instruction operating on the<br>mm registers, not #UD. |

| #NM             | If TS in CR0 is set.                                                                                                                                                                                                                                      |

| #MF             | (64-bit operations only) If there is a pending x87 FPU exception.                                                                                                                                                                                         |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                                                                                                                   |

| #AC(0)          | (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3.                                                                                                               |

#### **Real-Address Mode Exceptions**

| #GP(0) | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.                                                                                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | If any part of the operand lies outside of the effective address space from 0 to FFFFH.                                                                                                                                                                   |

| #UD    | If EM in CR0 is set.                                                                                                                                                                                                                                      |

|        | 128-bit operations will generate #UD only if OSFXSR in CR4 is 0. Execu-<br>tion of 128-bit instructions on a non-SSE2 capable processor (one that is<br>MMX technology capable) will result in the instruction operating on the<br>mm registers, not #UD. |

| #NM    | If TS in CR0 is set.                                                                                                                                                                                                                                      |

| #MF    | (64-bit operations only) If there is a pending x87 FPU exception.                                                                                                                                                                                         |

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

#PF(fault-code) For a page fault.

#AC(0) (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made.

# PADDUSB/PADDUSW—Add Packed Unsigned Integers with Unsigned Saturation

| Opcode      | Instruction             | Description                                                                                         |

|-------------|-------------------------|-----------------------------------------------------------------------------------------------------|

| 0F DC /r    | PADDUSB mm, mm/m64      | Add packed unsigned byte integers from <i>mm/m64</i> and mm and saturate the results.               |

| 66 0F DC /r | PADDUSB xmm1, xmm2/m128 | Add packed unsigned byte integers from <i>xmm2/m128</i> and <i>xmm1</i> saturate the results.       |

| 0F DD /r    | PADDUSW mm, mm/m64      | Add packed unsigned word integers from <i>mm/m64</i> and mm and saturate the results.               |

| 66 0F DD /r | PADDUSW xmm1, xmm2/m128 | Add packed unsigned word integers from<br><i>xmm2/m128</i> to <i>xmm1</i> and saturate the results. |

#### Description

Performs an SIMD add of the packed unsigned integers from the source operand (second operand) and the destination operand (first operand), and stores the packed integer results in the destination operand. See Figure 9-4 in the *IA-32 Intel Architecture Software Developer's Manual, Volume 1* for an illustration of an SIMD operation. Overflow is handled with unsigned saturation, as described in the following paragraphs.

These instructions can operate on either 64-bit or 128-bit operands. When operating on 64-bit operands, the destination operand must be an MMX technology register and the source operand can be either an MMX technology register or a 64-bit memory location. When operating on 128-bit operands, the destination operand must be an XMM register and the source operand can be either an XMM register or a 128-bit memory location.

The PADDUSB instruction adds packed unsigned byte integers. When an individual byte result is beyond the range of an unsigned byte integer (that is, greater than FFH), the saturated value of FFH is written to the destination operand.

The PADDUSW instruction adds packed unsigned word integers. When an individual word result is beyond the range of an unsigned word integer (that is, greater than FFFFH), the saturated value of FFFFH is written to the destination operand.

#### Operation

PADDUSB instruction with 64-bit operands:

$DEST[7..0] \leftarrow SaturateToUnsignedByte(DEST[7..0] + SRC (7..0]);$

\* repeat add operation for 2nd through 7th bytes \*:

DEST[63..56] ← SaturateToUnsignedByte(DEST[63..56] + SRC[63..56]

PADDUSB instruction with 128-bit operands:

DEST[7-0]  $\leftarrow$  SaturateToUnsignedByte (DEST[7-0] + SRC[7-0]);

\* repeat add operation for 2nd through 14th bytes \*:

$DEST[127-120] \leftarrow SaturateToUnSignedByte (DEST[127-120] + SRC[127-120]);$

PADDUSW instruction with 64-bit operands:

DEST[15..0] "SaturateToUnsignedWord(DEST[15..0] + SRC[15..0] );

\* repeat add operation for 2nd and 3rd words \*: DEST[63..48] <sup>°°</sup> SaturateToUnsignedWord(DEST[63..48] + SRC[63..48] );

PADDUSW instruction with 128-bit operands:

DEST[15-0] SaturateToUnsignedWord (DEST[15-0] + SRC[15-0]); \* repeat add operation for 2nd through 7th words \*: DEST[127-112] ← SaturateToUnSignedWord (DEST[127-112] + SRC[127-112]);

### Intel C/C++ Compiler Intrinsic Equivalents

| m64 _mm_adds_pu8(m64 m1,m64 m2)        |

|----------------------------------------|

| m64 _mm_adds_pu16(m64 m1,m64 m2)       |

| m128i _mm_adds_epu8 (m128i a,m128i b)  |

| m128i _mm_adds_epu16 (m128i a,m128i b) |

|                                        |

## **Flags Affected**

None.

## **Protected Mode Exceptions**

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.                                                                                                                                                                 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.                                                                                                                                                |

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                                                                                                                                                                    |

| #UD             | If EM in CR0 is set.                                                                                                                                                                                                                                      |

|                 | 128-bit operations will generate #UD only if OSFXSR in CR4 is 0. Execu-<br>tion of 128-bit instructions on a non-SSE2 capable processor (one that is<br>MMX technology capable) will result in the instruction operating on the<br>mm registers, not #UD. |

| #NM             | If TS in CR0 is set.                                                                                                                                                                                                                                      |

| #MF             | (64-bit operations only) If there is a pending x87 FPU exception.                                                                                                                                                                                         |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                                                                                                                   |

| #AC(0)          | (64-bit operations only) If alignment checking is enabled and an unaligned memory reference is made while the current privilege level is 3.                                                                                                               |

#### **Real-Address Mode Exceptions**

| #GP(0) | (128-bit operations only) If a memory operand is not aligned on a 16-byte boundary, regardless of segment.                                                                                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | If any part of the operand lies outside of the effective address space from 0 to FFFFH.                                                                                                                                                                   |

| #UD    | If EM in CR0 is set.                                                                                                                                                                                                                                      |

|        | 128-bit operations will generate #UD only if OSFXSR in CR4 is 0. Execu-<br>tion of 128-bit instructions on a non-SSE2 capable processor (one that is<br>MMX technology capable) will result in the instruction operating on the<br>mm registers, not #UD. |

| #NM    | If TS in CR0 is set.                                                                                                                                                                                                                                      |

| #MF    | (64-bit operations only) If there is a pending x87 FPU exception.                                                                                                                                                                                         |